ADV7181

Video A/D-Wandler, verbaut in Navigationssystemen mit Videoeingang für Rückfahrkamera.

Fotos und Position

Technische Daten

- Hersteller: Analog Devices

- PDF-Datenblatt

- I2C Schnittstelle zur Programmierung

- IO-Signalpegel: 3,3 V

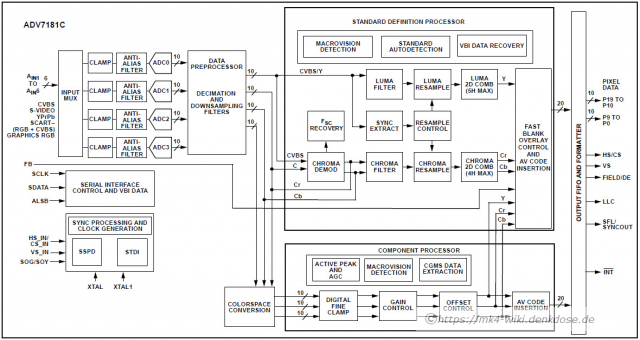

Blockdiagramm und typisches Anwendungsbeispiel

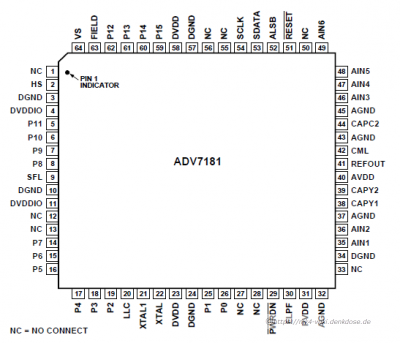

Pinout

Programmierung

Initialisierung durch Cyclone III FPGA auf MCA-Plus Grafikboard

IDENT

Das IDENTITY-Register 0x11 gibt bei diesem Chip den Wert 0x19 zurück. Die Software verwendet den Zugriff darauf um zu prüfen ob der Chip antwortet, vorhanden oder bereits aus einem RESET zurückgekehrt ist.

20 11 19

RESET

40 0F 80= Store 0x80 into register 0x0F = Start reset sequence (takes approx. 2 ms)

SETUP 1

40 07 7B⇒ Set Autodetect Enable Register0x07to0b0111_1011- Detect PAL B/G/I/H, PAL N, PAL 60, NTSC, NTSC443 formats

40 15 00⇒ Set Digital Clamp Control 1 Register0x15to0b0000_0000- Slow (TC = 1 s)

40 17 41⇒ Set Shaping Filter Control Register0x17to0b0100_0001- Auto narrow notch for poor quality sources or wideband filter with comb for good quality input. Select Chrominance Filter „SH1“ for all video standards and for good and bad video.

40 1D 40⇒ Set UNKNOWN Register0x1Dto0b0100_000040 0F 40⇒ Set Power Management Register0x0Fto0xb0100_0000RESERVEDVALUE IN DATASHEET

40 3A 16⇒ Set ADC Control Register0x3Ato0b0001_0110- Power down ADC2

- Power down ADC1

- Set ADC0 to normal operation

40 3D C3⇒ Set Manual Window Register0x3Dto0b1100_0011- Kill at 8.5%

40 3F E4⇒ Set UNKNOWN Register0x3Fto0b1110_010040 50 04⇒ Set CTI DNR Control 4 Register0x50to0b0000_0100- Set to 0x04 for A/V input

40 51 2D⇒ Set Lock Count Register0x51to0b0_0_101_101- Count-into-lock = 500 lines of video

- Count-out-of-lock = 500 lines of video

- Over field with vertical info

- Lock status set only by horizontal lock

40 C4 80⇒ Set ADC SWITCH 2 Register0xC4to0b1_000_0000- Enable manual setting of the input signal muxing

40 0E 80⇒ Set ADI Control Register0x0Eto0b1_1_00_00_00- Set sync signals to „Low drive strength (1x)“

- Set clock signal to „Low drive strength (1x)“

- Enable LLC pin to be three-stated

40 50 20⇒ Set CTI DNR Control 4 Register0x50to0b0010_0000(ILLEGAL: VALUE)40 52 18⇒ Set UNKNOWN Register0x52to0b0001_100040 58 ED⇒ Set UNKNOWN Register0x58to0b1110_110140 77 C5⇒ Set UNKNOWN Register0x77to0b1100_010140 7C 93⇒ Set UNKNOWN Register0x7Cto0b1001_001140 7D 00⇒ Set UNKNOWN Register0x7Dto0b0000_000040 90 C9⇒ Set VBI Info Read Mode Details Register0x90to0b1100_1_0_0_1(ILLEGAL: READ ONLY)40 91 40⇒ Set WSS1 Register0x91to0b0100_0000(ILLEGAL: READ ONLY)40 92 3C⇒ Set WSS2 Register0x92to0b0011_1100(ILLEGAL: READ ONLY)40 93 CA⇒ Set EDTV1 Register0x93to0b0011_1100(ILLEGAL: READ ONLY)40 94 D5⇒ Set EDTV2 Register0x94to0b1101_0101(ILLEGAL: READ ONLY)40 CF 50⇒ Set UNKNOWN Register0xCFto0b0101_000040 D0 4E⇒ Set UNKNOWN Register0xD0to0b0100_111040 D6 DD⇒ Set UNKNOWN Register0xD6to0b1101_110140 E5 51⇒ Set NTSC V Bit Begin Register0xE5to0b0_1_0_10001- Set „V“ high after 30 lines from „Icount“ rollover (default: 5 lines)

- Set „NVBEGSIGN“ to low

- Set „NVBEGDELE“ to additional delay by 1 line

- Set „NVBEGDELO“ to no delay

40 D5 A0⇒ Set UNKNOWN Register0xD5to0b1010_000040 D7 EA⇒ Set UNKNOWN Register0xD7to0b1110_101040 E4 3E⇒ Set SD Saturation Cr Register0xE4to0b0011_111040 E9 3E⇒ Set PAL V Bit End Register0xE9to0b0_0_1_11110- Set „V“ high after 30 lines from „Icount“ rollover (default: 5 lines)

- Set „PVENDSIGN“ to 1

- Set „PVENDDELE“ to no delay

- Set „PVENDDELO“ to no delay

40 EA 0F⇒ Set PAL F Bit Toggle Register0xEAto0b0_0_0_01111- Set toggle „F“ signal after 15 lines after „Icount“ rollover (default: 3 lines)

- Set to „PFTOGSIGN“ to low

- Set „PFTOGDELE“ to no delay

- Set „PFTOGDELO“ to no delay

40 0E 00⇒ Set ADI Control Register0x0Eto0b0_0_00_00_00- Set „DR_STR_S“ to Low drive strength

- Set „DR_STR_C“ to Low drive strength

- Set LLC pin active

40 C3 06⇒ Set ADC SWITCH 1 Register0xC3to0b0000_0110- No input selected

40 0A 0A⇒ Set Brightness Register0x0Ato0b0000_1010- 0x0A equals „8 IRE“

20 11 19⇒ Read IDENT Register0x11having value0b0001_1001

SETUP 2

Nach der Squenz „SETUP 1“ folgt dieselbe Sequenz erneut, wird aber durch folgende ergänzt:

40 0E 20⇒ Set ADI Control Register0x0Eto0b0_0_10_00_00- Set LLC pin to „three-stated“

40 4C 02⇒ Set Gemstar Control 5 Register0x4Cto0b0000001_0- Split data into half byte

40 40 D2⇒ Set UNKNOWN Register0x40to0b1101_001040 0E 00⇒ Set ADI Control Register0x0Eto0b0_0_00_00_00- Set LLC pin to „active“

40 0E 20⇒ Set ADI Control Register0x0Eto0b0_0_10_00_00- Set LLC pin to „three-stated“

40 4B 02⇒ Set Gemstar Control 4 Register0x4Bto0b0000001_040 0E 00⇒ Set ADI Control Register0x0Eto0b0_0_00_00_00- Set LLC pin to „active“

20 11 19⇒ Read IDENT Register0x11with value0b0001_100140 0E 20⇒ Set ADI Control Register0x0Eto0b0_0_10_00_00- Set LLC pin to „three-stated“

20 49 06⇒ Read Gemstar Control 2 Register0x49having value0b0000_011040 0E 00⇒ Set ADI Control Register0x0Eto0b0_0_00_00_00- Set LLC pin to „active“

20 10 0F⇒ Read Status Register0x10having value0b0000_111120 13 29⇒ Read Status Register 3 Register0x13having value0b0010_100120 0A 00⇒ Read Brightness Register0x0Ahaving value0b0000_000020 08 80⇒ Read Contrast Register0x08having value0b1000_0000- Gain = 1 dB

20 0B 00⇒ Read Hue Register0x0Bhaving value0b0000_000020 E3 80⇒ Read SD Saturation Cb having value0b1000_0000- Chroma gain = 0 dB

Fundort im Flash-Memory des Graphicboard

Tatsächlich liegen diese Sequenzen fest vorgegeben im Flash auf dem Graphicboard und im „fgs.dnl“ File der Update-CD:

Offset(h) 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F

0007AEF0 40 07 7B 40 15 00 40 17 41 40 1D 40 40 0F 40 40 @.{@..@.A@.@@.@@

0007AF00 3A 16 40 3D C3 40 3F E4 40 50 04 40 51 2D 40 C4 :.@=Ã@?ä@P.@Q-@Ä

0007AF10 80 40 0E 80 40 50 20 40 52 18 40 58 ED 40 77 C5 €@.€@P @R.@Xí@wÅ

0007AF20 40 7C 93 40 7D 00 40 90 C9 40 91 40 40 92 3C 40 @|“@}.@.É@‘@@’<@

0007AF30 93 CA 40 94 D5 40 CF 50 40 D0 4E 40 D6 DD 40 E5 “Ê@”Õ@ÏP@ÐN@ÖÝ@å

0007AF40 51 40 D5 A0 40 D7 EA 40 E4 3E 40 E9 3E 40 EA 0F Q@Õ @×ê@ä>@é>@ê.

0007AF50 40 0E 00 40 00 05 40 03 0C 40 04 77 40 17 41 40 @..@..@..@.w@.A@

0007AF60 1D 47 40 31 02 40 3A 17 40 3B 81 40 3D A2 40 3E .G@1.@:.@;.@=¢@>

0007AF70 6A 40 3F A0 40 86 0B 40 F3 01 40 F9 03 40 0E 80 j@? @†.@ó.@ù.@.€

0007AF80 40 52 46 40 54 00 40 7F FF 40 81 30 40 90 C9 40 @RF@T.@.ÿ@.0@.É@

0007AF90 91 40 40 92 3C 40 93 CA 40 94 D5 40 B1 FF 40 B6 ‘@@’<@“Ê@”Õ@±ÿ@¶

0007AFA0 08 40 C0 9A 40 CF 50 40 D0 4E 40 D1 B9 40 D6 DD .@Àš@ÏP@ÐN@ѹ@ÖÝ

0007AFB0 40 D7 E2 40 E5 51 40 F6 3B 40 0E 00 40 01 C8 40 @×â@åQ@ö;@..@.È@

0007AFC0 05 00 40 06 0E 40 1D 40 40 0F 40 40 31 02 40 3A ..@..@.@@.@@1.@:

0007AFD0 10 40 3D C3 40 3F E4 40 52 00 40 53 00 40 54 07 .@=Ã@?ä@R.@S.@T.

0007AFE0 40 55 0C 40 56 94 40 57 89 40 58 48 40 59 08 40 @U.@V”@W‰@XH@Y.@

0007AFF0 5A 00 40 5B 7A 40 5C E1 40 5D 00 40 5E 19 40 5F Z.@[z@\á@].@^.@_

0007B000 48 40 60 08 40 61 00 40 62 20 40 63 03 40 64 A9 H@`.@a.@b @c.@d©

0007B010 40 65 1A 40 66 B8 40 67 03 40 68 00 40 6A 80 40 @e.@f¸@g.@h.@j€@

0007B020 6B C3 40 73 D0 40 74 B4 40 7B 06 40 C3 C9 40 C4 kÃ@sÐ@t´@{.@ÃÉ@Ä

0007B030 8D 40 85 1A 40 86 02 40 B3 FE 40 C9 0C 40 0E 80 .@….@†.@³þ@É.@.€

0007B040 40 58 ED 40 90 C9 40 91 40 40 92 3C 40 93 CA 40 @Xí@.É@‘@@’<@“Ê@

0007B050 94 D5 40 CF 7C 40 D0 4E 40 D6 DD 40 E5 51 40 0E ”Õ@Ï|@ÐN@ÖÝ@åQ@.

Offset(h) 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F

004E1090 40 07 7B 40 @.{@

004E10A0 15 00 40 17 41 40 1D 40 40 0F 40 40 3A 16 40 3D ..@.A@.@@.@@:.@=

004E10B0 C3 40 3F E4 40 50 04 40 51 2D 40 C4 80 40 0E 80 Ã@?ä@P.@Q-@Ä€@.€

004E10C0 40 50 20 40 52 18 40 58 ED 40 77 C5 40 7C 93 40 @P @R.@Xí@wÅ@|“@

004E10D0 7D 00 40 90 C9 40 91 40 40 92 3C 40 93 CA 40 94 }.@.É@‘@@’<@“Ê@”

004E10E0 D5 40 CF 50 40 D0 4E 40 D6 DD 40 E5 51 40 D5 A0 Õ@ÏP@ÐN@ÖÝ@åQ@Õ

004E10F0 40 D7 EA 40 E4 3E 40 E9 3E 40 EA 0F 40 0E 00 40 @×ê@ä>@é>@ê.@..@

004E1100 00 05 40 03 0C 40 04 77 40 17 41 40 1D 47 40 31 ..@..@.w@.A@.G@1

004E1110 02 40 3A 17 40 3B 81 40 3D A2 40 3E 6A 40 3F A0 .@:.@;.@=¢@>j@?

004E1120 40 86 0B 40 F3 01 40 F9 03 40 0E 80 40 52 46 40 @†.@ó.@ù.@.€@RF@

004E1130 54 00 40 7F FF 40 81 30 40 90 C9 40 91 40 40 92 T.@.ÿ@.0@.É@‘@@’

004E1140 3C 40 93 CA 40 94 D5 40 B1 FF 40 B6 08 40 C0 9A <@“Ê@”Õ@±ÿ@¶.@Àš

004E1150 40 CF 50 40 D0 4E 40 D1 B9 40 D6 DD 40 D7 E2 40 @ÏP@ÐN@ѹ@ÖÝ@×â@

004E1160 E5 51 40 F6 3B 40 0E 00 40 01 C8 40 05 00 40 06 åQ@ö;@..@.È@..@.

004E1170 0E 40 1D 40 40 0F 40 40 31 02 40 3A 10 40 3D C3 .@.@@.@@1.@:.@=Ã

004E1180 40 3F E4 40 52 00 40 53 00 40 54 07 40 55 0C 40 @?ä@R.@S.@T.@U.@

004E1190 56 94 40 57 89 40 58 48 40 59 08 40 5A 00 40 5B V”@W‰@XH@Y.@Z.@[

004E11A0 7A 40 5C E1 40 5D 00 40 5E 19 40 5F 48 40 60 08 z@\á@].@^.@_H@`.

004E11B0 40 61 00 40 62 20 40 63 03 40 64 A9 40 65 1A 40 @a.@b @c.@d©@e.@

004E11C0 66 B8 40 67 03 40 68 00 40 6A 80 40 6B C3 40 73 f¸@g.@h.@j€@kÃ@s

004E11D0 D0 40 74 B4 40 7B 06 40 C3 C9 40 C4 8D 40 85 1A Ð@t´@{.@ÃÉ@Ä.@….

004E11E0 40 86 02 40 B3 FE 40 C9 0C 40 0E 80 40 58 ED 40 @†.@³þ@É.@.€@Xí@

004E11F0 90 C9 40 91 40 40 92 3C 40 93 CA 40 94 D5 40 CF .É@‘@@’<@“Ê@”Õ@Ï

004E1200 7C 40 D0 4E 40 D6 DD 40 E5 51 40 0E 00 00 00 00 |@ÐN@ÖÝ@åQ@.....