Dies ist eine alte Version des Dokuments!

OMAP5948

Hintergrundinfos

Der OMAP5948 wird in den Bosch/Blaupunkt Navigationssystemen als sog. HMI-Prozessor (HMI = Human-Machine-Interface) verwendet. „OMAP“ ist die englische Abkürzung für „Open Multimedia Application Platform“ und bezeichnet eine Mikrocontroller-Produktlinie von Texas Instruments (TI). Es handel sich um ein SOC-System (SOC = System-On-Chip), womit ein Chip bezeichnet wird, der für sich allein bereits lauffähig ist.

Er wurde speziell für Bosch entwickelt und produziert und ist somit nicht auf dem freien Markt verfügbar. Ebensowenig wie Dokumentationen dazu. Er entspricht jedoch dem OMAP5912, für den es zahlreiche Unterlagen und Infos im Netz gibt. Alle nachfolgenden Informationen basieren auf dieser These. Wer mehr darüber weiß, oder gar ein Datenblatt besitzt dem wäre ich sehr dankbar wenn er sich über das Kontaktformular bei mir meldet!

SOC-Aufbau

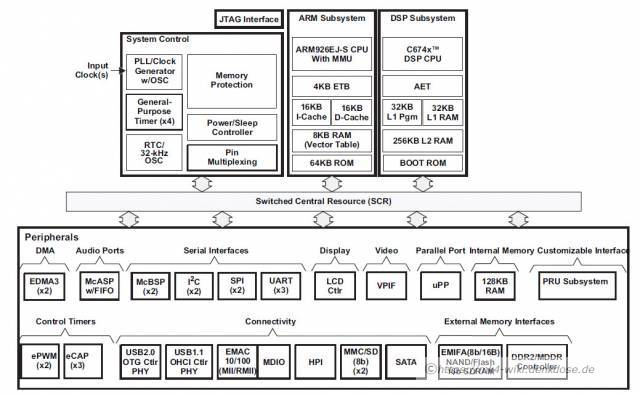

Der Chip enthält neben einer ARM-CPU und einem DSP auch noch viele weitere Komponenten, wie diese Blockgrafik verdeutlicht:

Nicht alle davon kommen in den Navigationssystemen zum Einsatz. Die Betriebs- und Signal (IO) Spannung beträgt 1,6V und der Chip kann mit maximal 192 MHz getaktet werden. Da für die internen Komponenten nicht jeder Pin einzeln rausgeführt wird, sind etliche Pins im „Multiplex“ belegt. D.H. je nach Softwarekonfiguration des Chips kann der Pin eine andere Funktion haben. Erkennbar ist dies an Pinbezeichnungen die durch Schrägstrich getrennt sind, z.B. MPUIO1/RTCK/SPIF.SCK. Dieser Pin könnte also intern entweder mit einem generischen IO-Port der CPU (MPUIO1), einem Signal des JTAG-Controllers (RTCK) oder mit dem Taktsignal einer SPI-Schnittstelle (SPIF.SCK) verbunden sein.

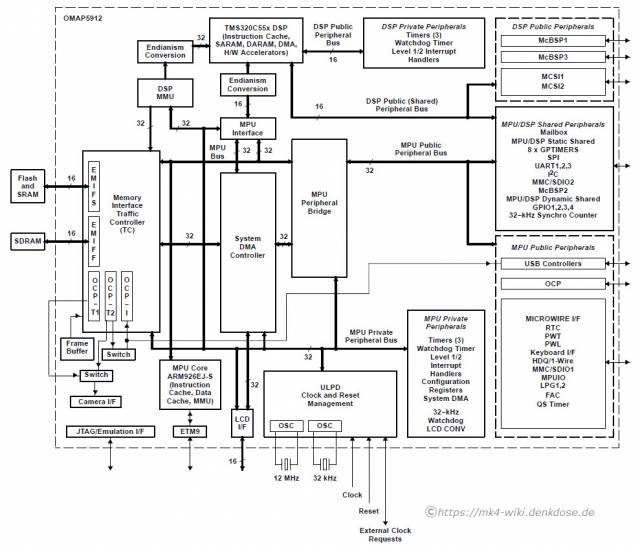

Dieses Schaubild zeigt einen funktionalen Überblick des Chips:

Die ARM-CPU (MPU)

Der CPU im OMAP entspricht dem Typ ARM926EJ-S und damit der ARM-Architektur ARMv5TEJ. Diese versteht zwei Befehlssätze (Mnemonics): ARM (32-Bit Instructions) und Thumb (16-Bit Instructions) und kann 8, 16 oder 32-Bit Daten verarbeiten und wird ausschließlich im Little Endian Modus betrieben.

Die CPU-Einheit besitzt eine Daten- und Programm-Speicherverwaltungseinheit (MMU), sowie einen Coprocessor 15 (CP15) and protection module. Dieser erkennt z.B. Programmabstürze oder unzulässige Speicherzugriffe.

Die JTAG-ID der CPU lautet 0x0692602F, die IRLEN beträgt 4 Bit. Der IRPre (Offset) im OMAP ist 38 Bit.

Die OMAP32_ID lautet 0x03320500, was die Typen „POMAP5912“ oder „OMAP5912B“ in Revision 2.2 identifiziert.

Der DSP (Digital-Signal-Processor)

Der DSP ist ein TMS320C55x (C55x) und besitzt z.B. Video Hardware Accelerators für DCT, iDCT, Pixel Interpolation, sowie Motion Estimation für Video-Compression.

Das Memory-Interface

Hierüber werden externe Speicher verwaltet.

''EMIFS'' ("External-Memory-Interface-Slow")

Hierüber werden externe Flash-Speicher oder statische RAMs (SRAM) angebunden. Diese Schnittstelle bietet einen 16-Bit breiten Datenbus, sowie 4 Chip-Select Signale. Der Adressbus ist 25 Bit breit und somit in der Lage Speicherbausteine bis max. 64M-Bytes zu nutzen. Die maximale Gesamtkapazität liegt somit bei 4×64 = 256M-Byte.

''EMIFF'' ("External-Memory-Interface-Fast")

Dient zur Ankopplung von dynamischen RAMs (SDRAM). Der Datenbus ist 16-Bit und der Adressbus 25-Bit breit (max. 64M-Byte). Über zwei Bank-Select Bits können also maximal 4x 64M-Byte (=256M-Byte) an externem SDRAM angesprochen werden.

Das JTAG-Interface

Der OMAP bietet ein IEEE 1149.1 konformes JTAG-Interface an.

JTAG_CHAIN = 8, 4, 38 ; list of IR lenghts of all TAP controller in JTAG chain

Datenblatt

- Gehäuseform: BGA 289

- Aufdruck: „OMAP5948GXF“

- Hersteller: TI (Texas Instruments)